Googleの研究員であるローリー・ワイアード氏が、60年前から存在しているDRAMの欠陥を克服するためのライブラリ「Tailslayer」を公開しました。

GitHub – LaurieWired/tailslayer: Library for reducing tail latency in RAM reads · GitHub

https://github.com/LaurieWired/tailslayer

Your RAM Has a 60 Year Old Design Flaw. I Bypassed It. – YouTube

コンピューターのメモリとして広く使用されているDRAMは、キャパシタに蓄えられた電荷の有無で「0」と「1」を判別する仕組みです。キャパシタ内の電荷は時間と共に失われるため、電荷を一度読み出して書き込み直す「リフレッシュ」という作業を一定時間ごとに行い続ける必要があります。

リフレッシュの作業中はメモリへアクセスすることができず、CPUがメモリにアクセスしようとした際にDRAMがリフレッシュ作業中だった場合、数百ナノ秒から数マイクロ秒の待機時間が発生してしまいます。この問題は1966年にDRAMが考案された時から長期に渡って存在していました。

多くの人にとって数百ナノ秒がどれくらいの長さなのかを実感することは難しいものの、CPUのクロック数でいうと数千クロックを捨てている計算に。リアルタイム性を特に重視する金融などの分野で問題になっていました。なお、コンピューター内部での数百ナノ秒がどんな長さなのかについては以下の記事を読むと把握できます。

プログラマーが知っておくべき「PC内部の通信速度」 – GIGAZINE

Tailslayerは、メモリに書き込む際に複数の独立したDRAMチャネルにデータを複製します。そして読み込みの際には複製先の全てのアドレスに読み取り命令を出し、一番最初に読み込めたデータを採用するという仕組み。リフレッシュ中のメモリからデータが読めずとも、複数配置したデータのどれかがリフレッシュ中でなければ長い待ち時間は発生しないというわけです。

「複数の独立したDRAMチャネル」に書き込む方法を編み出すため、ワイアード氏はメモリコントローラーが物理アドレスをどのように扱っているかを統計的なタイミング測定を用いて特定。データが異なるチャネルに配置されるよう、チャネルスクランブリングオフセットを用いて書き込みを行うと述べています。

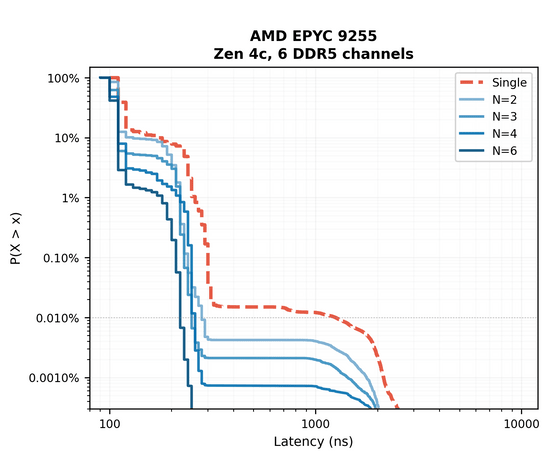

AMD EPYC 9255におけるTailslayerを使用した際のレイテンシーの違いは下図の通り。横軸がレイテンシーで縦軸がそのレイテンシーが現れる頻度を示しています。赤い点線はTailslayerを使用しなかった場合のレイテンシーの分布です。青線はTailslayerを使用した場合の分布で、2つに複製しただけの場合から6つに複製した場合までを4段階の濃さで表示しています。Tailslayerを使うとレイテンシーを抑えることが可能で、6箇所に複製する設定では最悪の場合でもレイテンシーを250ナノ秒程度に抑えることに成功しました。

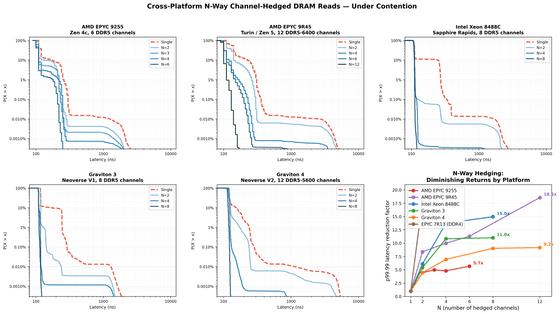

AMD、Intel、GravitonなどさまざまなCPUとメモリの組み合わせで違いを確かめた結果は下図の通り。いずれの場合でも、Tailslayerを使用して6個に複製した場合にはレイテンシーのスパイクを回避できていることが分かります。

ワイアード氏によると、99.99パーセンタイル点でのレイテンシーは最大で15分の1まで削減できたとのこと。高頻度取引(HFT)のような極めてわずかな遅延が大きな影響を与える分野で活用できるはずだと述べました。

この記事のタイトルとURLをコピーする

ソース元はコチラ

この記事は役に立ちましたか?

もし参考になりましたら、下記のボタンで教えてください。